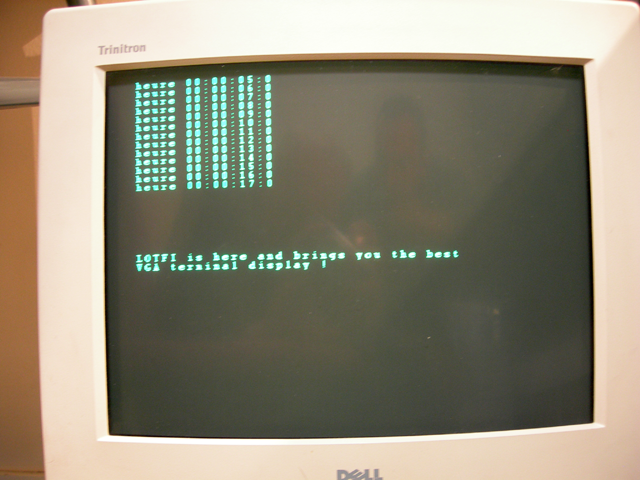

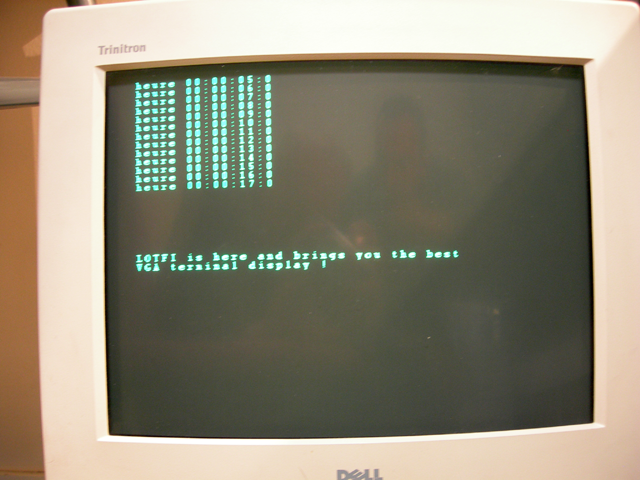

Affichage sur le moniteur (le temps de pose sans flash a rendu la photo floue)

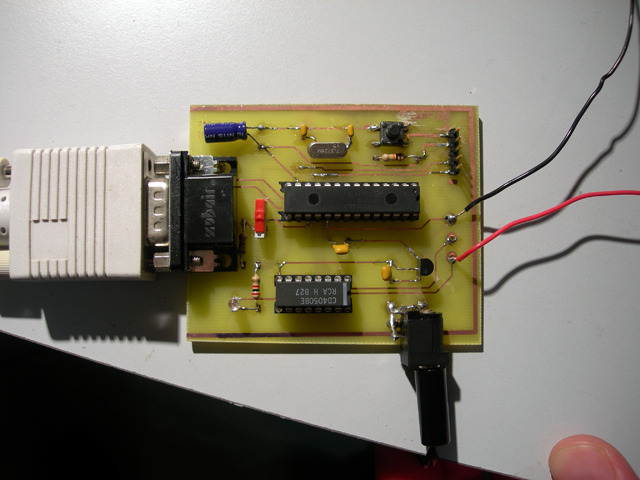

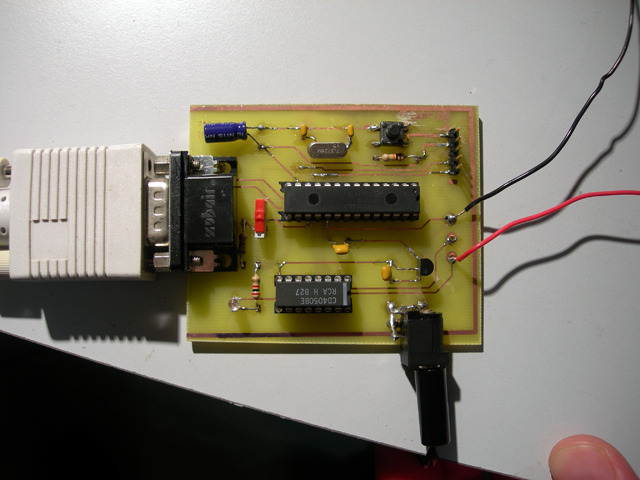

Carte du montage

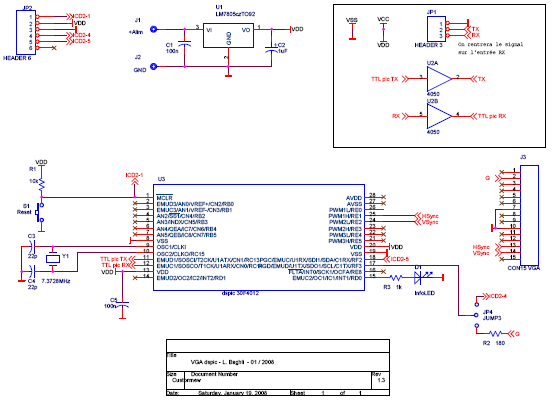

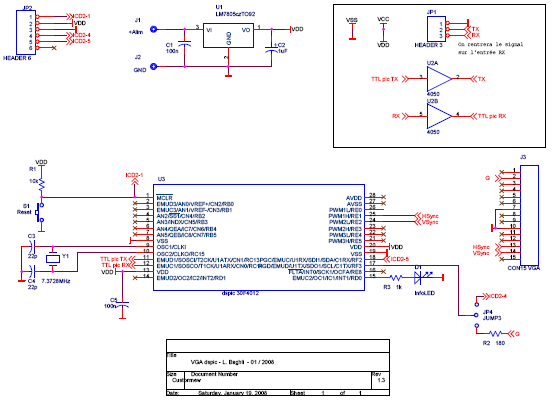

Schéma électronique (version RX à 5V ou 3.3V)

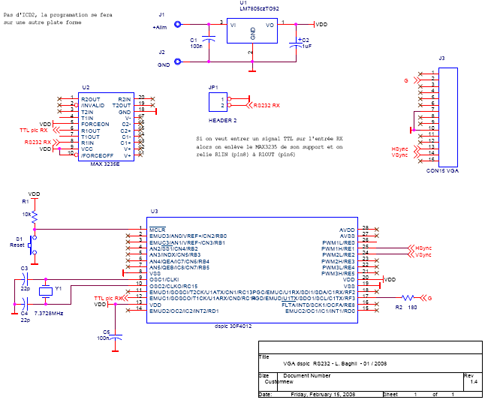

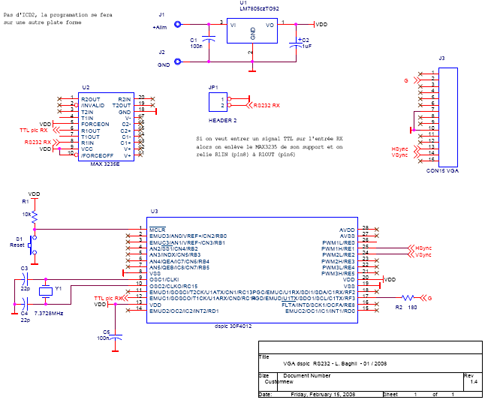

Schéma électronique (version RX en RS232 19200 BAUDS)

|

|

|

hsync_off; //HSYNC syncro level off |

hsync_off; //HSYNC syncro level off |

//Make Vsync length 2 VGA lines if ((linecount == 10 )||(linecount == 11 )) vsync_on; //Make here vertical syncronization & HSYNC syncro level on else vsync_off; //.. & HSYNC syncro level on |

if (++y_line_render == vga_symbol_height) { raw_render++; y_line_render = 0; } |

hsync_off; //HSYNC syncro level off for (j=0; j<28; j++) __builtin_nop(); |

// render ici pour être sûr d être synchrone if(video_enable_flg) { if (raw_render > vga_row_countm1) raw_render=vga_row_countm1; //on est ds la zone visible, alors : render _ptr = &str_array[raw_render * vga_symbols_per_row]; //Set pointer for render line (display bufffer) _ptr1 = &symbol[0][y_line_render]; //Set pointer for render line (character generator) //Cycle for render line j = vga_symbols_per_row; video_on; // pour débug while(j--) { SPI1BUF = ~(*(_ptr1 + (* _ptr++)*vga_symbol_height)); SPI1BUF = 0; // pour effacer le bit restant, mais il faut aller vite } video_enable_flg=0; video_off; // pour débug } |

|

Last update : 15/02/2007